The ability for a CPU to process several assembly commands at the same time.

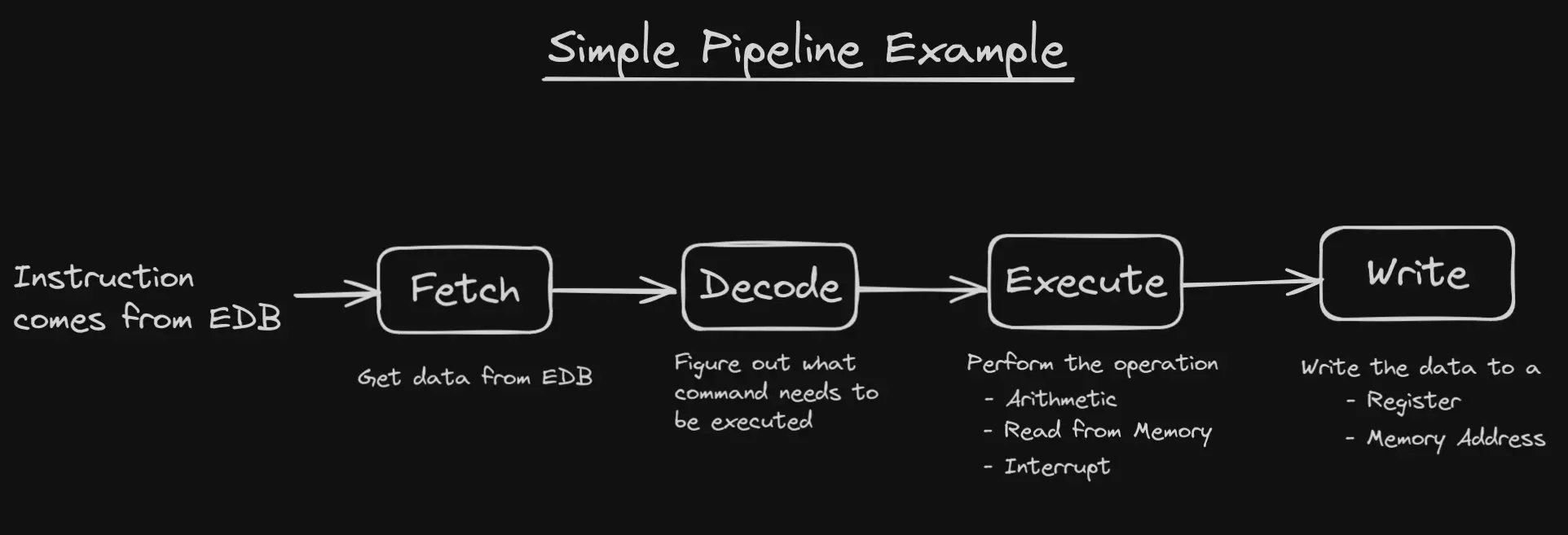

Pipelines

Assembly commands are broken up into tasks. There are specific circuits responsible for a each task

This way, circuits can work when the other circuits are working too, rather then relying on the entire operation to finish.

Assembly commands are broken up into tasks. There are specific circuits responsible for a each task

This way, circuits can work when the other circuits are working too, rather then relying on the entire operation to finish.

Pipeline Stall

Certain commands take more than once clock cycle to complete. When this happens, the pipeline is stalled and must wait for the bottleneck to finish.

Pipeline Optimization

Cache/SRAM

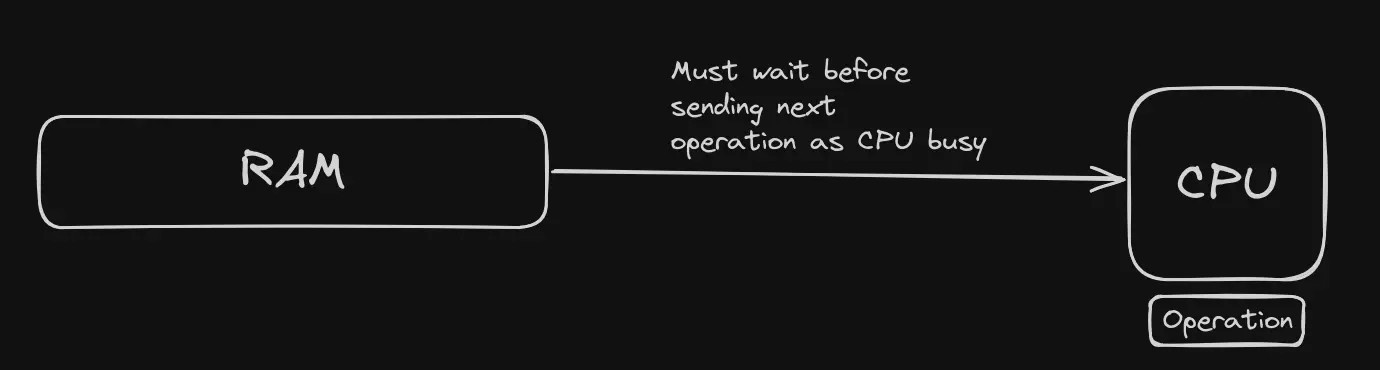

Pipe lining will always occur in CPU, leading to desynchronization between RAM and CPU, where the RAM must wait to send the next instruction.

This leads to later delay when the CPU finishes its operation, it must wait for the RAM to send over the operation

This leads to later delay when the CPU finishes its operation, it must wait for the RAM to send over the operation

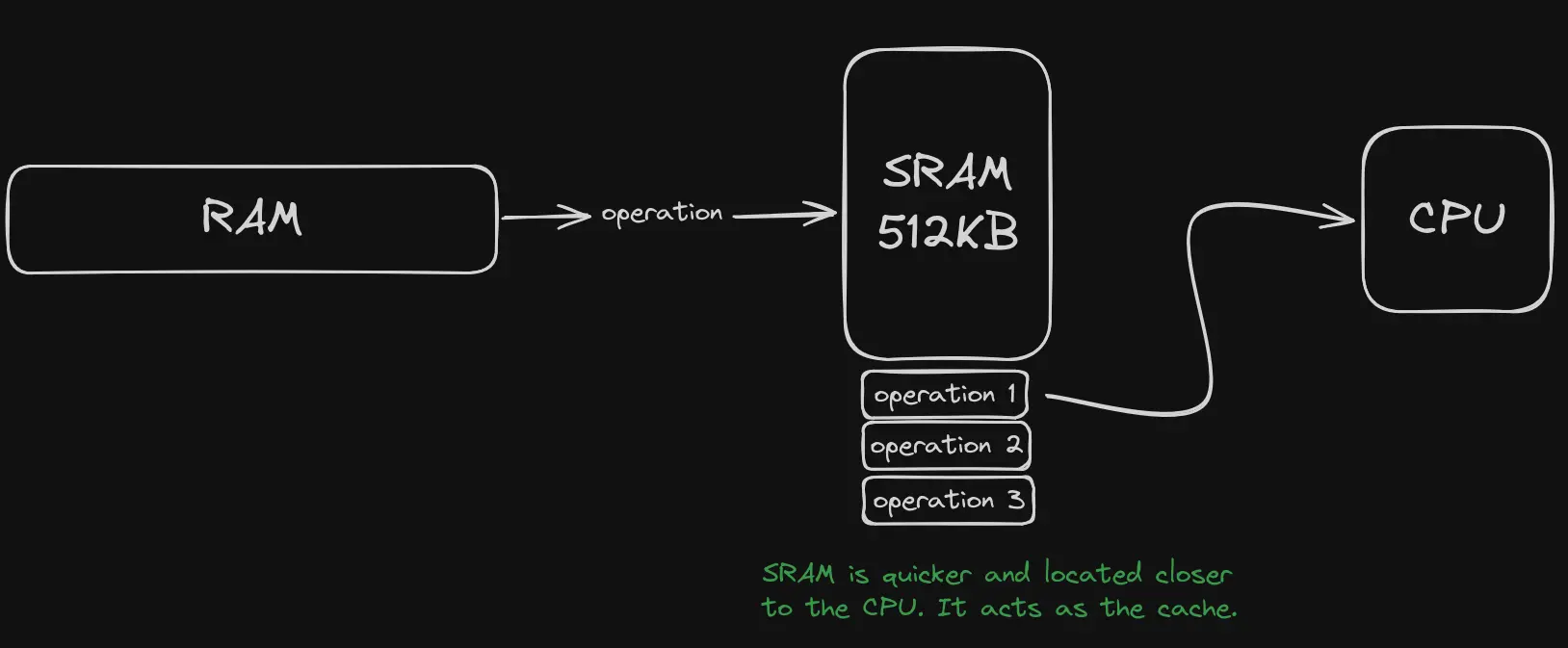

We never want to CPU to be idle, so to reduce wait states, SRAM is introduced.

We never want to CPU to be idle, so to reduce wait states, SRAM is introduced.

Many modern CPUs use multiple caches L1, L2, L3.

Each core contains their own L1 and L2 caches, the entire CPU shares the L3 cache.

Intel calls this Smart Cache

Many modern CPUs use multiple caches L1, L2, L3.

Each core contains their own L1 and L2 caches, the entire CPU shares the L3 cache.

Intel calls this Smart Cache

Multithreading

Ability to run multiple threads at the same time, effectively creating multiple CPUs.